**Department of Electrical Engineering**

Govt. Polytechnic Nabarangpur- 764059

# LABORATORY MANUAL

## **Digital Electronics & Microprocessor Lab**

## (5th Semester)

Prepared By: Deepika Sarkar

## Department of Electronics Engineering

Govt. Polytechnic Nabarangpur

## **TABLE OF CONTENTS**

| SI. No | Name of theExperiment                                          | Pages |

|--------|----------------------------------------------------------------|-------|

| 1      | To verify all the logic gates.                                 |       |

| 2      | Universal properties of NAND & NOR gates.                      | 5-7   |

| 3      | Implementation of half adder and Full adder using logic gates. | 8-12  |

| 4      | Implementation of half & full subtracter using logic gates.    | 16-19 |

| 5      | Implementation of a 4-bit Binary to Gray code converter.       | 20-24 |

| 6      | Implementation of a Single bit digital comparator              | 24-26 |

| 7      | To study Multiplexer and demultiplexer.                        | 27-28 |

| 8      | Study of flipflops                                             | 29-30 |

| 9      | Realize 4 bit asynchronous counter                             | 30-31 |

| 10     | Realize 4 bit synchronous counter                              |       |

| 11     | Implement mod-10 asynchronous counter                          |       |

| 12     | Study of shift register                                        | 32-33 |

|    |                                                                 | - |

|----|-----------------------------------------------------------------|---|

| 13 | 1s complement & 2s complement.                                  |   |

|    |                                                                 |   |

| 14 | Addition and subtraction of 2 8 bit numbers.                    |   |

| 15 | Decimal addition & subtraction of of 8 bit numbers.             |   |

| 15 | Decimal addition & subtraction of of o bit numbers.             |   |

| 16 | Comparision between 2 numbers and find the largest in an array. |   |

| 17 | Block transfer.                                                 |   |

| 18 | Traffic light control using 8255.                               |   |

| 19 | Generation of square wave using 8255.                           |   |

|    |                                                                 |   |

5

| Date: | / | _/ |  |

|-------|---|----|--|

|-------|---|----|--|

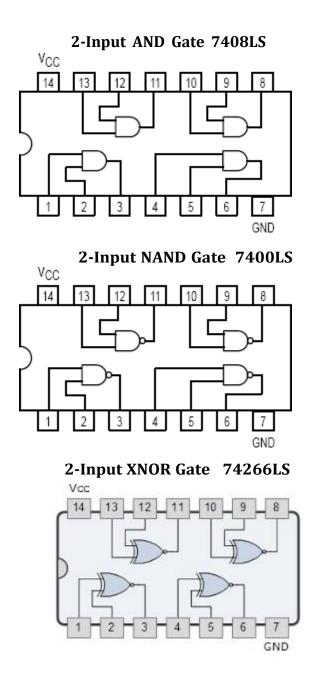

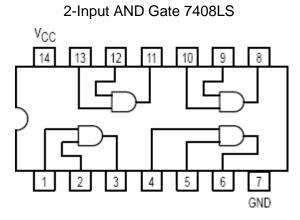

<u>Aim: -</u> To Verify truth tables of AND, OR, NOT, NOR, NAND, XOR, XNOR gates.

Apparatus Required: -

**1**.All the basic gates mention in the fig. 2.IC Trainer Kit

#### Procedure: -

- 1. Place the IC on IC Trainer Kit.

- **2.** Connect  $V_{CC}$  and ground to respective pins of IC Trainer Kit.

- Connect the inputs to the input switches provided in the IC Trainer Kit.

- 4. Connect the outputs to the switches of O/P LEDs,

- **5.** Apply various combinations of inputs according to the truth table and observe condition of LEDs.

- **6.** Disconnect output from the LEDs and note down the corresponding multimeter voltage readings for various combinations of inputs.

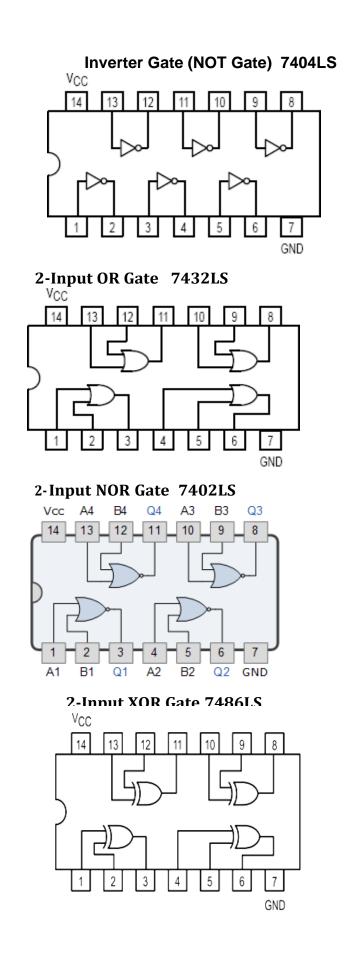

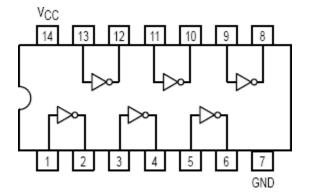

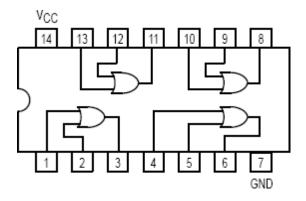

Inverter Gate (NOT Gate) 7404LS

| А | O/P |

|---|-----|

| 0 | 1   |

| 1 | 0   |

6

| А | В | O/P |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

2-Input OR Gate 7432LS

| А | В | O/P |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

| А | В | O/P |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

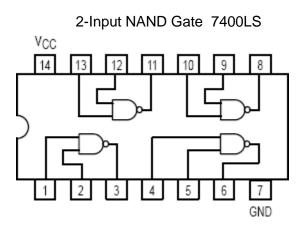

#### 2-Input NOR Gate 7402LS

7

| 1 | А | В | O/P |

|---|---|---|-----|

|   |   |   |     |

|   | 0 | 0 | 1   |

|   | 0 | 1 | 0   |

|   | 1 | 0 | 0   |

|   | 1 | 1 | 0   |

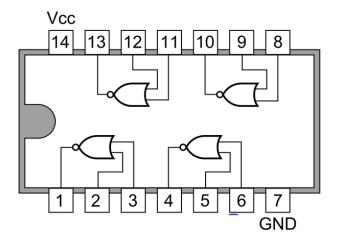

2-Input XOR Gate 7486LS

| А | В | O/P |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

| А | В | O/P |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

<u>Conclusion:-</u> Truth table of logic gates are verified.

8

Date: \_\_/ /

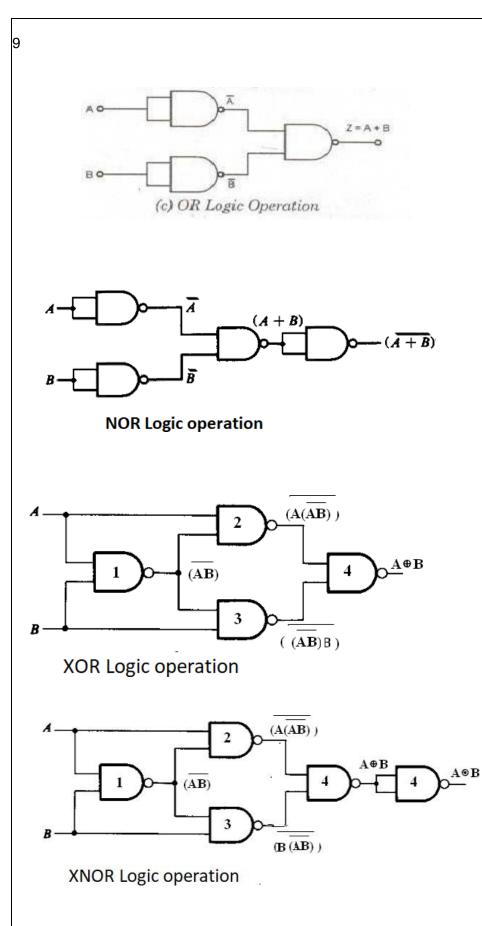

<u>Aim:</u> - Implementation of various gates by using universal properties of NAND & NOR gates and

Verify truth table.

#### **APPARATUS REQUIRED**

- 1. Digital IC trainer kit

- 2. IC 7400 (NAND gate)

- 3. IC 7402(NOR gate)

#### THEORY:

NAND OR NOR gates are sufficient for the realization of any logic expression. because of this reason, NAND and NOR gates are known as UNIVERSAL gates.

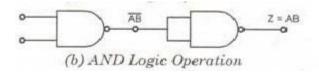

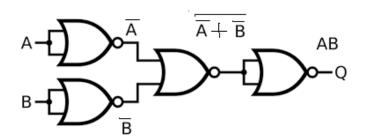

1. For NAND gate as universal gate

#### **PROCEDURE:**

- 1. Make the connections as per the logic diagram.

- 2. Connect +5v to pin 14 & ground to pin 7 of IC 7400

- 3. Apply diff combinations of inputs to the i/p terminals.

- 4. Note o/p for NAND as universal gate.

- 5. Verify the truth table.

O Z=Ā

(a) NOT Logic Operation

| Α | Ā |

|---|---|

| 0 | 1 |

| 1 | 0 |

| В | AB          |

|---|-------------|

| 0 | 0           |

| 1 | 0           |

| 0 | 0           |

| 1 | 1           |

|   | 0<br>1<br>0 |

| А | В | A+B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

| А | В | A+B |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 0   |

| А | В | A⊕B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

| А | В | AOB |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

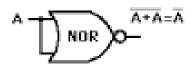

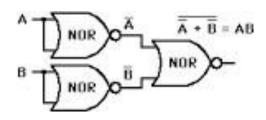

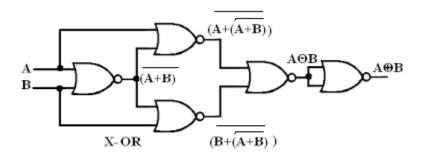

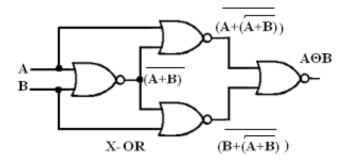

#### 2.For NOR gate as universal gate

#### **PROCEDURE:**

- 1. Make the connections as per the logic diagram.

- 2. Connect +5v to pin 14 & ground to pin 7 of IC 7402

- 3. Apply diff combinations of inputs to the i/p terminals.

- 4. Note o/p for NAND as universal gate.

- 5. Verify the truth table

**NOT Logic operation**

A

Ā

0

1

1

0

A

B

A+B

0

0

0

0

1

1

1

0

1

1

1

1

**OR Logic operation**

AND Logic operation

NAND Logic operation

| А | В | AB |

|---|---|----|

| 0 | 0 | 0  |

| 0 | 1 | 0  |

| 1 | 0 | 0  |

| 1 | 1 | 1  |

| А | В | AB |

|---|---|----|

| 0 | 0 | 1  |

| 0 | 1 | 1  |

| 1 | 0 | 1  |

| 1 | 1 | 0  |

| А | В | A⊕B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

## **XOR Logic operation**

11

| А | В | AOB |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

#### <u>Conclusion:-</u>

We have constructed and verified truth table of all gates using universal gates NAND and NOR gate.

```

Date: __/_/

```

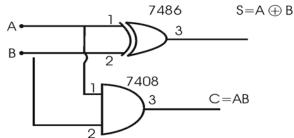

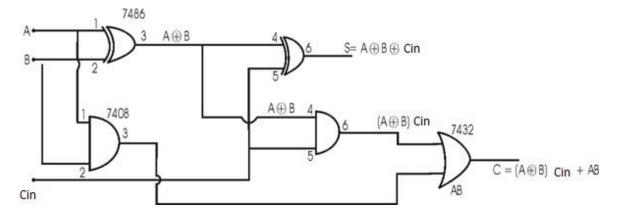

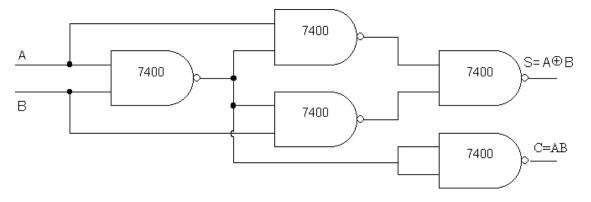

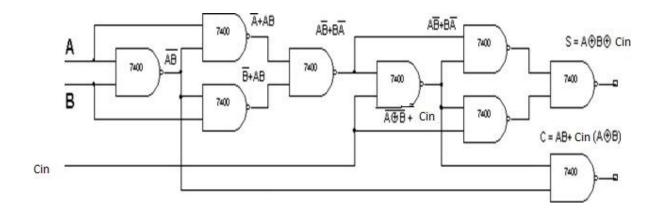

<u>Aim: -</u> Implementation of half adder and Full adder using logic gates.

#### **APPARATUS REQUIRED**

1.IC 7486, IC 7432, IC 7408, IC 7400. 2.Digital trainer kit.

#### THEORY:

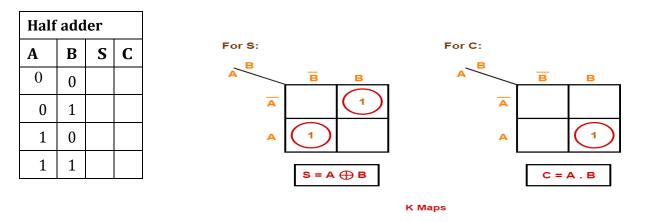

**Half-Adder:** A combinational logic circuit that performs the addition of two data bits, A and B, is called a half-adder. Addition will result in two output bits; one of which is the sum bit, S, and the other is the carry bit, C. The Boolean functions describing the half-adder are:

$S = A \bigoplus B$  C = A B

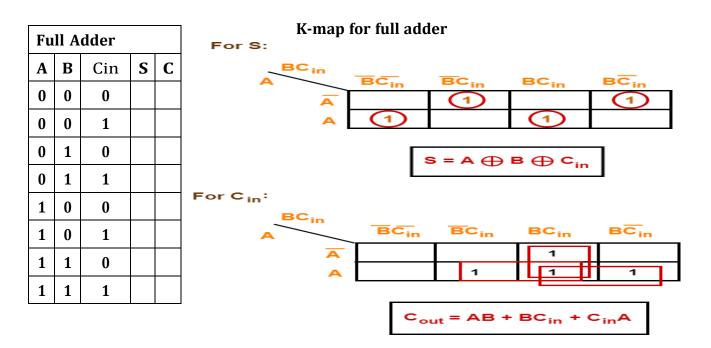

**Full-Adder:** The half-adder does not take the carry bit from its previous stage into account. This carry bit from its previous stage is called carry-in bit. A combinational logic circuit that adds two data bits, A and B, and a carry-in bit, Cin, is called a full-adder. The Boolean functions describing the full-adder are:

$S = (x \bigoplus y) \bigoplus C_{in}$   $C = xy + C_{in} (x \bigoplus y)$

#### Procedure: -

- 1. Verify the gates.

- 2. Make the connections as per the circuit diagram.

- 3. Switch on  $V_{CC}$  and apply various combinations of input according to the truth table.

- 4. Note down the output readings for half and full adder sum and the carry bit for different combinations of inputs.

#### Half Adder using basic gates:-

#### Full Adder using basic gates:-

#### Half Adder using NAND gates only:-

#### Full Adder using NAND gates only:-

#### K-map for half adder

### <u>Conclusion: -</u>

Half adder and full adder are constructed and their truth tables are verified.

15

Date: \_\_/\_/\_\_

<u>Aim: -</u> Implementation of half subtractor and Full subtractor using logic gates.

#### **APPARATUS REQUIRED**

1.IC 7486, IC 7432, IC 7408,IC7404, IC7400. 2.Digital trainer kit.

#### THEORY:

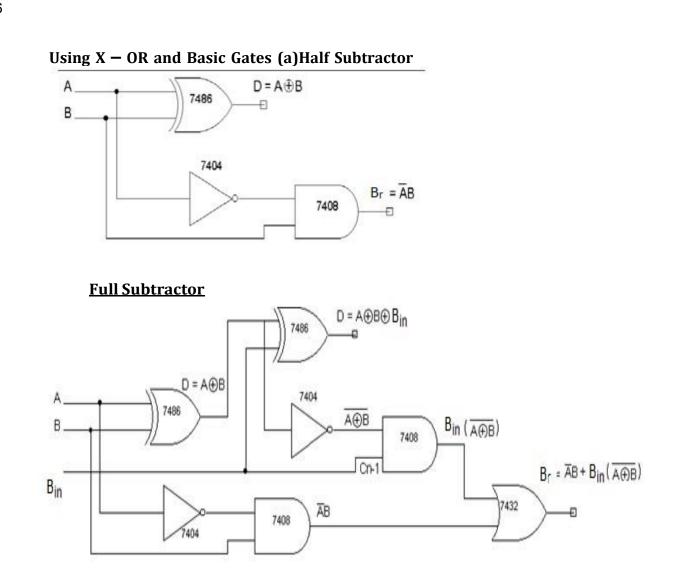

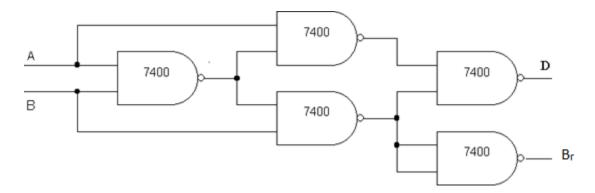

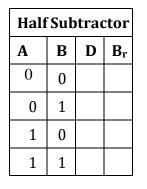

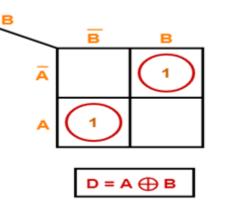

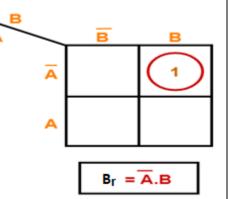

**Half Subtractor:** Subtracting a single-bit binary value B from another A (i.e. A -B) produces a difference bit D and a borrow out bit B-out. This operation is called half subtraction and the circuit to realize it is called a half subtractor. The Boolean functions describing the halfSubtractor are:

$$D = A \bigoplus B \qquad \qquad B_r = \overline{A} B$$

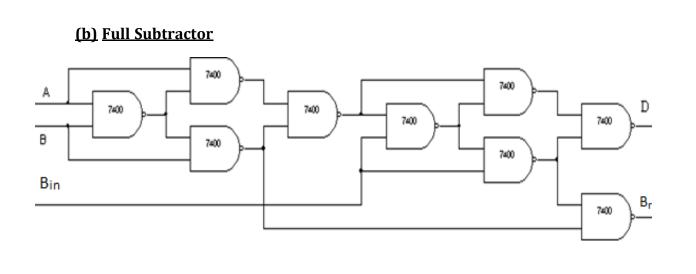

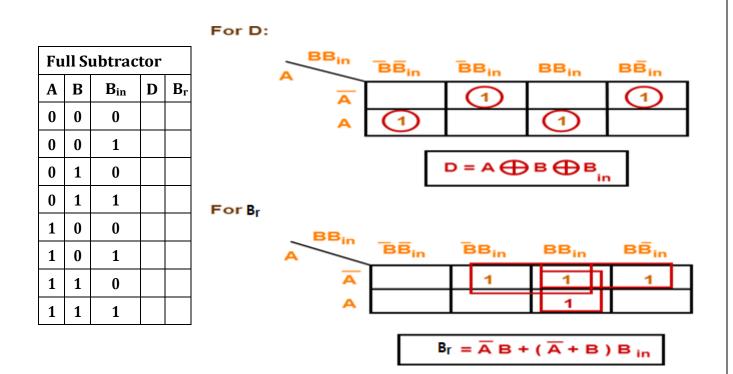

**Full Subtractor:** Subtracting two single-bit binary values, B, Cin from a single-bit value A produces a difference bit D and a borrow out Br bit. This is called full subtraction. The Boolean functions describing the full-subtracter are:

$$D = (x \bigoplus y) \bigoplus B_{in} \qquad B_r = \overline{A}B + \overline{A} (B_{in}) + B (B_{in})$$

#### Procedure: -

- 1. Verify the gates.

- 2. Make the connections as per the circuit diagram.

- 3. Switch on  $V_{CC}$  and apply various combinations of input according to the truth table.

- 4. Note down the output readings for half and full subtractor difference and borrow bit for different combinations of inputs.

#### Using only NAND gate (a) Half subtractor

K Maps

Conclusion: -

Half subtractor and full subtractor are constructed and their truth tables are verified.

Date: \_\_/\_/\_\_

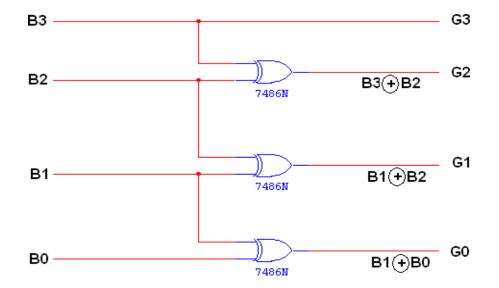

<u>Aim: -</u> Implementation of a 4-bit Binary to Gray code converter.

#### APPARATUS REQUIRED

IC 7486

Digital trainer kit

#### THEORY:

Gray Code is one of the most important codes. It is a non-weighted code which belongs to a class of codes called minimum change codes.

In this codes while traversing from one step to another step, only one bit in the code group changes.

The input variable are designated as B3, B2, B1, B0 and the output variables are designated as G3, G2, G1, G0.

#### Procedure: -

- 1. The circuit connections are made as shown in fig.

- 2. Pin (14) is connected to +Vcc and Pin (7) to ground.

- 3. In the case of binary to gray conversion, the inputs B0, B1, B2 and B3 are given at respective pins and outputs G0, G1, G2, G3 are taken for all the 16 combinations of the input.

- 4. The values of the outputs are tabulated.

#### TRUTH TABLE:

| Binary Input Gray code output |    |    |    |  |    |    |    |    |

|-------------------------------|----|----|----|--|----|----|----|----|

| B3                            | B2 | B1 | B0 |  | G3 | G2 | G1 | G0 |

| 0                             | 0  | 0  | 0  |  | 0  | 0  | 0  | 0  |

| 0                             | 0  | 0  | 1  |  | 0  | 0  | 0  | 1  |

| 0 | 0 | 1 | 0                                     | 0 | 0 | 1 | 1 |

|---|---|---|---------------------------------------|---|---|---|---|

| 0 | 0 | 1 | 1                                     | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0                                     | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1                                     | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0                                     | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1                                     | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0                                     | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1                                     | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0                                     | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1                                     | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0                                     | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1                                     | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0                                     | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1                                     | 1 | 0 | 0 | 0 |

| L |   | • | · · · · · · · · · · · · · · · · · · · |   |   |   |   |

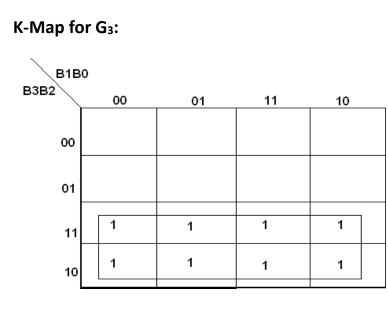

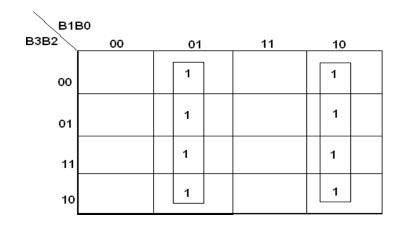

K-Map for G<sub>2</sub>:

G2 = B3⊕B2

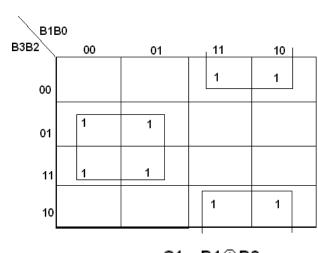

K-Map for G<sub>0</sub>:

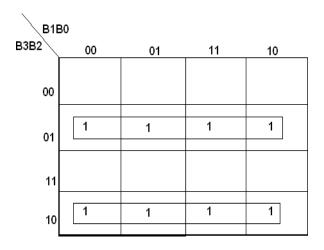

K-Map for G<sub>1</sub>:

G0 = B1⊕B0

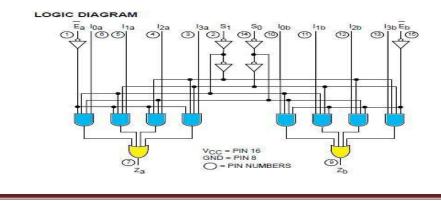

#### LOGIC DIAGRAM

#### Conclusion: -

4-bit Binary to Gray code converter is constructed and their truth tables are verified.

Date: \_\_/\_/\_\_

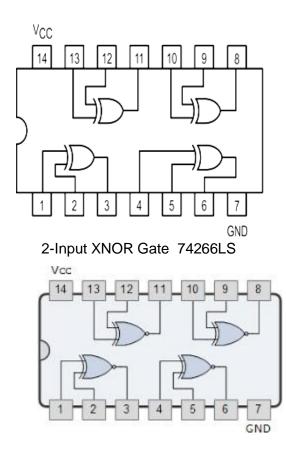

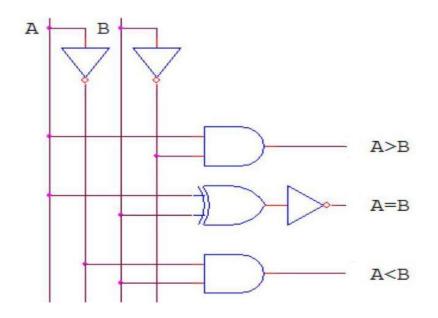

<u>Aim: -</u> Implementation of a Single bit digital comparator.

#### **APPARATUS REQUIRED**

1. IC 7404,IC 7408,IC 74266 2. Digital trainer kit

#### THEORY:

Magnitude Comparator is a logical circuit, which compares two signals A and B and generates three logical outputs, whether A > B, A = B, or A < B.

#### Procedure: -

- 1. The circuit connections are made as shown in fig.

- 2. Pin (14) is connected to +Vcc and Pin (7) to ground.

- 3. The inputs A,B are given at respective pins and outputs A > B, A = B, or A < B are connected to the output LED.

- 4. The values of the outputs are tabulated.

| INP | UTS | OUTPUTS |       |       |  |  |  |

|-----|-----|---------|-------|-------|--|--|--|

| Α   | В   | A > B   | A = B | A < B |  |  |  |

| 0   | 0   | 0       | 1     | 0     |  |  |  |

| 0   | 1   | 0       | 0     | 1     |  |  |  |

| 1   | 0   | 1       | 0     | 0     |  |  |  |

| 1   | 1   | 0       | 1     | 0     |  |  |  |

#### **TRUTH TABLE**

$A > B = A \overline{B}$  $A < B = \overline{A} B$  $A = B = \overline{A} B + AB$

#### LOGIC DIAGRAM

#### Conclusion: -

A Single bit digital comparator is constructed and it's truth tables are verified.

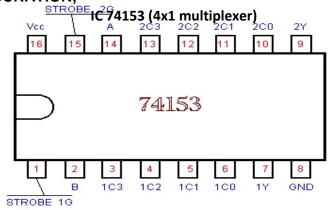

Date: \_\_/\_/\_

<u>Aim: -</u> To study Multiplexer and demultiplexer.

#### **APPARATUS REQUIRED:** Power Supply

Digital Trainer, Connecting Leads, IC's 74153(4x1 multiplexer).

#### THEORY:

**MULTIPLEXER:** Multiplexer generally means many into one. A multiplexer is a circuit with many Inputs but only one output. By applying control signals we can steer any input to the output .The fig. (1) Shows the general idea. The ckt. has n-

input signal, control signal & one output signal. Where  $2^n = m$ . One of the popular multiplexer is the

16 to 1 multiplexer, which has 16 input bits, 4 control bits & 1 output bit.

#### **PIN CONFIGURATION;-**

#### LOGIC DIAGRAM:

#### Multiplexer (4x1) IC 74153

**PROCEDURE:**

- Fix the IC's on the bread board &give the input supply.

Make connection according to the circuit.

- Give select signal and strobe signal at respective pins.

Connect +5 v Vcc supply at pin no 24 &

- GND atpin no 12.

- 5. Verify the truth table for various inputs.

#### **OBSERVATION TABLE:**

#### Truth Table of multiplexer (4x1) IC 74153

|                       | INPUT             |                  |        |         |        |        |          |                   |

|-----------------------|-------------------|------------------|--------|---------|--------|--------|----------|-------------------|

|                       | A B C0 C1 C2 C3 G |                  |        |         |        |        | Yo       |                   |

|                       | X                 | X                | X      | X       | X      | X      | .3       | 0                 |

|                       | 0                 | 0                | 0      | X       | X      | X      | 0        | 0                 |

|                       | <b>0</b> 0        | <b>0</b> 0       | 1      | - *X*   | °X:    | X      | -0       | <u></u> ]         |

|                       | 0                 | ্ব               | X      |         | X      | X      | 0        | 0.                |

|                       | 0                 | ্য               | ×      | -1j     | ×      | X      | 0        | . į               |

| Conclusion: Verify th | e trut            | h t <u>a</u> ble | e of m | ultiple | xer fo | r yari | ouş in   | puts <sub>0</sub> |

|                       | া                 | 0                | ×      | X       | ્યું   | X      | <u>0</u> | 1                 |

|                       | ٦                 | 1                | X      | ×       | X      | 0      | 0        | 0                 |

|                       | Π.                | - î              | X      | X       | X      | 1      | 0        | 1                 |

Date: \_\_/\_/\_

Aim: - To study SR Flipflops .

**APPARATUS REQUIRED:** IC' S 7400, 7402 Digital Trainer & Connecting leads.

#### THEORY:

• **<u>RS FLIP-FLOP:</u>** There are two inputs to the flip-flop defined as R and S. When I/Ps R = 0 and S = 0 then O/P remains unchanged. When I/Ps R = 0 and S = 1 the flip-flop is switches to the stable state where O/P is 1 i.e. SET. The I/P condition

is R = 1 and S = 0 the flip-flop is switched to the stable state where O/P is 0 i.e. RESET. The I/P condition is R = 1 and S = 1 the flip-flop is switched to the stable state where O/P is forbidden.

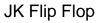

- <u>JK FLIP-FLOP</u>: For purpose of counting, the JK flip-flop is the ideal element to use. The variable J and K are called control I/Ps because they determine what the flip- flop does when a positive edge arrives. When J and K are both 0s, both AND gates are disabled and Q retains its last value.

- <u>D FLIP –FLOP</u>: This kind of flip flop prevents the value of D from reaching the Q output until clock pulses occur. When the clock is low, both AND gates are disabled D can change value without affecting the value of Q. On the other hand, when the clock is high, both AND gates are enabled. In this case, Q is forced to equal the value of D. When the clock again goes low,Q retains or stores the last value of D. a D flip flop is a bistable circuit whose D input is transferred to the output after a clock pulse is received.

- <u>T FLIP-FLOP</u>: The T or "toggle" flip-flop changes its output on each clock edge, giving an output which is half the frequency of the signal to the T input. It is useful for constructing binary counters, frequency dividers, and general binary addition devices. It can be made from a J-K flip-flop by tying both of its inputs high.

CIRCUIT DIAGRAM: SR Flip Flop

D Flip Flop

### DIGITAL E LECTRO NICS

#### **PROCEDURE:**

- 1. Connect the circuit as shown in fi gure.

- 2. Apply Vc c & ground signal to every IC.

- 3. Observe the input & output according to the truth table.

#### TRUTH TABL E: SR F LIP FLOP:

| СГОСК | S | R | Q<br>n+1   |

|-------|---|---|------------|

| 1     | 0 | 0 | NO CH ANGE |

| 1     | 0 | 1 | 0          |

| 1     | 1 | 0 | 1          |

| 1     | 1 | 1 | ?          |

#### D FL IPFLOP:

| INPUT | OU TPUT |  |  |

|-------|---------|--|--|

| 0     | 0       |  |  |

| 1     | 1       |  |  |

#### JK FLIPFLOP

| CLOCK | S | R | Q<br>n+1   |  |

|-------|---|---|------------|--|

| 1     | 0 | 0 | NO CH ANGE |  |

| 1     | 0 | 1 | 0          |  |

| 1     | 1 | 0 | 1          |  |

| 1     | 1 | 1 | Qn '       |  |

#### T FL IPFLOP

| CLOCK | S | R | Q<br>n+1   |

|-------|---|---|------------|

| 1     | 0 | 1 | NO CH ANGE |

| 1     | 1 | 0 | Qn '       |

#### 30

#### **Experiment No:9**

Date: \_\_/\_/\_\_

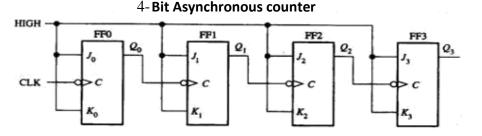

<u>Aim: -</u>Realize 4 bit asynchronous counter

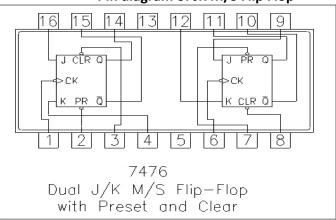

APPARATUS REQUIRED: Digital trainer kit 4 JK flip flop each IC 7476 (i.edual JK flip flop) and two AND gates IC 7408.

**BRIEF THEORY**: Counter is a circuit which cycle through state sequence. Two types of counter, Synchronous counter (e.g. parallel) and Asynchronous counter (e.g. ripple). In Ripple counter same flip-flop output to be used as clock signal source for other flip- flop. Synchronous counter use the same clock signal for all flip-flop.

#### **PIN CONFIGURATION:**

Pin diagram of JK M/S Flip Flop

#### LOGIC DIAGRAM:

LAB MANUAL (IV SEM ECE)

LAB MANUAL (IV SEM ECE)

| Pin Number | Description          |  |  |

|------------|----------------------|--|--|

| 1          | Clock 1 Input        |  |  |

| 2          | Preset 1 Input       |  |  |

| 3          | Clear 1 Input        |  |  |

| 4          | J1 Input             |  |  |

| 5          | Vcc                  |  |  |

| 6          | Clock 2 Input        |  |  |

| 7          | Preset 2 Input       |  |  |

| 8          | Clear 2 Input        |  |  |

| 9          | J2 Input             |  |  |

| 10         | Complement Q2 Output |  |  |

| 11         | Q2 Output            |  |  |

| 12         | K2 Input             |  |  |

| 13         | Ground               |  |  |

| 14         | Complement Q1 Output |  |  |

| 15         | Q1 Output            |  |  |

| 16         | K1 Input             |  |  |

#### **PROCEDURE:**

a) Make the connections as per the logic diagram.

b) Connect +5v and ground according to pin configuration.

c) Apply diff combinations of inputs to the i/p terminals.

d) Note o/p for summation.

e) Verify the truth table.

**RESULT:** 4-bit asynchronous counter studied and verified.

31

LAB MANUAL (IV SEM ECE)

#### DIGITAL E LECTRO NICS

#### 32

#### **Experiment No:12**

Date: \_\_/\_/\_\_

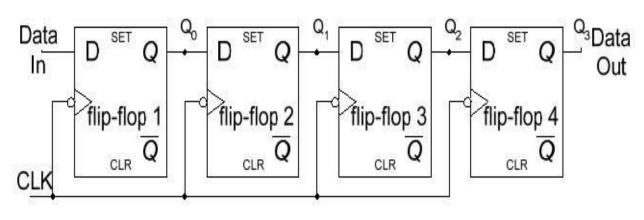

#### Aim: Design of 4-bit shift register . APPARATUS REQUIRED: - Logic trainer kit, D Flip-flop IC - 7474 wire

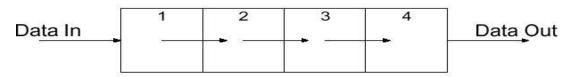

Theory: <u>Serial In/Serial Right/Serial Out Operation</u>

Serial shift registers can be implemented using any type of flip-flops. A serial shift register implemented using D flip-flops with the serial data applied at the D input of the first flip-flop and serial data out obtained at the Q output of the last flip-flop is shown in figure. At each clock transition 1 bit of serial data is shifted in and at the same instant 1-bit of serial data is shifted out. For a 4-bit shift register, 8 clock transitions are required to shift in 4-bit data and completely shift out the 4-bit data. As the data shifted out 1-bit at a time, a logic 0 value is usually shifted in to fillup the vacant bits in the shift register.

Serial In/Shift Right/Serial Out Register

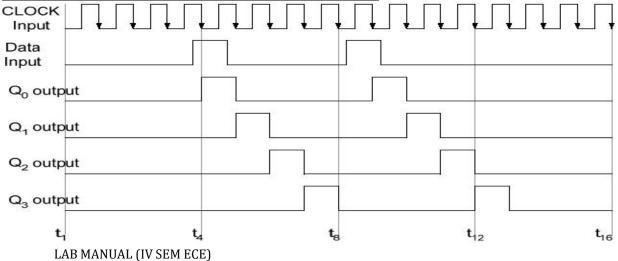

Timing diagram of a Serial In/Shift Right/Serial Out Register

## Shift Register Truth Table

| Outputs    | <b>Q</b> <sub>0</sub> | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> |

|------------|-----------------------|----------------|----------------|----------------|

| Reset      | 0                     | 0              | 0              | 0              |

| CK Pulse 1 | 1                     | 0              | 0              | 0              |

| CK Pulse 2 | 0                     | 1              | 0              | 0              |

| CK Pulse 3 | 0                     | 0              | 1              | 0              |

| CK Pulse 4 | 0                     | 0              | 0              | 1              |

#### **PROCEDURE:**

- (i) Connections are given as per circuit diagram.

- (ii) Logical inputs are given as per circuit diagram.

- $(\ensuremath{\textsc{iii}})$  Observe the output and verify the truth table.

#### **RESULT:**

Thus the Shift register was designed and their truth table is verified

LAB MANUAL (IV SEM ECE)